Qzone

Qzone

微博

微博

微信

微信

【PConline 资讯】2018年的SSD价格已经开始下降,更有一部分的SSD进入了1元1GB的价格。SSD的价格下降的同时,QLC闪存颗粒也开始进入市场,其相对较低的寿命与性能不经让一些玩家感到担忧。

近日,在旧金山的国际固态电路会议(ISSCC 2019)上,东芝宣布开发出可实现高速和大容量SSD的桥接芯片。与传统的无桥芯片方法相比,通过采用新开发的占用面积小、功耗低的桥接芯片,成功地用更少的高速信号线连接更多的闪存芯片。

在SSD中,主控需要连接多个闪存颗粒进行数据存储的控制,但随着闪存颗粒的数量越来越多,SSD的数据传输速度会降低,所以可连接的闪存颗粒是有限的。而为了增加容量,在需要增加接口数量的同时,也让更多的高速信号线连接到了主控上,这也增加了SSD的PCB布线难度。

B为桥接芯片,C为主控,N为闪存颗粒

东芝通过开发连接主控和闪存颗粒的桥接芯片克服了这个问题,其中包含了三种新技术:环形菊花链连接、使用PAM 4进行串行通信、用于消除桥芯片中的PLL电路的抖动改善技术。

菊花链连接的环形配置将桥接芯片所需要的收发器数量从两对减少到一对,让芯片面积减小;在主控和桥接芯片之间使用PAM 4进行串行通信,让桥接芯片内的电路操作速度减小,并且降低了收发器的性能要求;而使用具有PAM 4特性的新型CDR电路能改善抖动特性,并消除了桥接芯片对PLL电路的需求,从而缩小了桥接芯片的面积以及降低了功耗。

4条高速信号线运行速度可达25.6Gbps

通过使用这些技术,减少了桥接芯片的开销,并且可以仅使用少量高速信号线就让主控高速操作大量闪存芯片。原型桥接芯片采用28nm CMOS制程打造,并通过连接四个桥接芯片和环形菊花链中的主控来评估结果。所有桥接芯片和主控在25.6Gbps下的PAM 4通信下可以达到令人满意的性能,并且BER(比特误差)在10^-12以下。

东芝将继续进一步提高桥接芯片的性能,缩小面积和降低功耗,实现前所未有的高速和大容量存储。或许在这项技术的加持下,未来的SSD能使用中低端的主控实现更快的速度以及更大的容量,这无形也是一种惠及消费者的技术。原创 作者:月照蓝

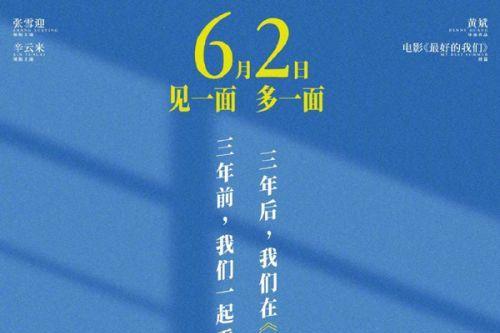

电影界2022-05-25 20:1905-25 20:19

电影界2022-05-25 20:1505-25 20:15

电影界2022-05-25 20:1505-25 20:15

电影界2022-05-25 19:5705-25 19:57